DISEÑO DE CIRCUITOS COMBINACIONALES

COMPETENCIA ESPECIFICA DE LA SESIÓN:

- Comprobar las tablas de verdad de puertas lógicas y sus combinaciones.

- Conocer las principales Puertas Lógicas, su simbología y comportamiento

- Utilizar un SIMULADOR para comprobar el comportamiento de los mismos.

- Utilizar métodos de simplificación de compuertas lógicas.

MARCO TEÓRICO:

| INPUT | OUTPUT | |

| A | B | A NAND B |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

La puerta NAND, compuerta NAND o NOT AND :

Es una puerta lógica que produce una salida falsa solamente si todas sus entradas son verdaderas; por tanto, su salida es complemento a la de la puerta AND, -se comporta de acuerdo a la tabla de verdad mostrada a la derecha. Cuando todas sus entradas están en 1 (uno) o en ALTA, su salida está en 0 o en BAJA, mientras que cuando una sola de sus entradas o ambas están en 0 o en BAJA, su SALIDA va a estar en 1 o en ALTA.

Se puede ver claramente que la salida X solamente es "0" (0 lógico, nivel bajo) cuando la entrada A como la entrada B están en "1". En otras palabras la salida X es igual a 0 cuando la entrada A y la entrada B son 1.

La puerta NAND es significativa debido a que cualquier función booleana se puede implementar mediante el uso de una combinación de puertas NAND. Esta propiedad se llama integridad funcional.

Los sistemas digitales que emplean ciertos circuitos lógicos se aprovechan de integridad funcional de NAND.

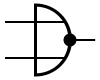

Simbolo:

|  |  |

| Símbolo ANSI o "Militar" | Símbolo IEC | Símbolo DIN |

| INPUT | OUTPUT | |

| A | B | A NOR B |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

La puerta NOR o compuerta NOR:

Es una puerta lógica digital que implementa la disyunción lógica negada -se comporta de acuerdo a la tabla de verdad mostrada a la derecha. Cuando todas sus entradas están en 0 (cero) o en BAJA, su salida está en 1 o en ALTA, mientras que cuando una sola de sus entradas o ambas están en 1 o en ALTA, su SALIDA va a estar en 0 o en BAJA. NOR es el resultado de la negación del operador OR. También puede ser visto como una puerta AND con todas las entradas invertidas. El NOR es una operación completamente funcional. Las puertas NOR se pueden combinar para generar cualquier otra función lógica. En cambio, el operador OR es monótono, ya que solo se puede cambiar BAJA a ALTA, pero no viceversa.

En la mayoría, pero no en todas, las implementaciones de circuitos, la negación viene libre—incluyendo CMOS y TTL. En tales familias lógicas, el OR es la operación más complicada; puede utilizar un NOR seguido de un NOT. Una excepción importante es que algunas formas de la familia lógica dominó.

Simbolo:

Símbolo ANSI o "Militar" Símbolo IEC Símbolo DIN

| INPUT | OUTPUT | |

| A | B | A XOR B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

La puerta XOR, compuerta XOR u OR exclusiva:

Es una puerta lógica digital que implementa el o exclusivo; es decir, una salida verdadera (1/HIGH) resulta si una, y solo una de las entradas a la puerta es verdadera. Si ambas entradas son falsas (0/LOW) o ambas son verdaderas, resulta en una salida falsa. La XOR representa la función de la desigualdad, es decir, la salida es verdadera si las entradas no son iguales, de otro modo el resultado es falso. Una manera de recordar XOR es "uno o el otro, pero no ambos".

La XOR también se puede ver como adición módulo 2. Como resultado, las puertas XOR se utilizan para implementar la adición binaria en las computadoras. Un semisumador consta de una puerta XOR y una puerta AND. También se utiliza como comparador y como inversor condicional.1

Las expresiones algebraicas ( ) representan ambas la puerta XOR con entradas A y B. El comportamiento de la XOR se resume en la tabla de verdad mostrada a la derecha.

| INPUT | OUTPUT | |

| A | B | A XNOR B |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

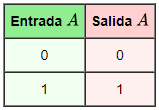

La puerta XNOR u OR

(a veces escrita "exnor" o "enor" y rara vez escrito NXOR) es una puerta lógica digital cuya función es la inversa de la puerta OR exclusiva (XOR). La versión de dos entradas implementa la igualdad lógica, comportándose de acuerdo a la tabla de verdad de la derecha. Una salida ALTA (1) resulta si ambas las entradas a la puerta son las mismas. Si una pero no ambas entradas son altas (1), resulta una salida BAJA (0).

Simbolo:

Símbolo XNOR "Distintivo" Símbolo XNOR "Rectangular"

Foto Grupal:

Observaciones:

- En el programa proteus se debe buscar

cada componente lógico mediante su código específico.

- Al momento de seleccionar los

componentes lógicos en el programa proteus, se escogió erróneamente

componentes similares a los necesarios para realizar el circuito.

- En la tabla de verdad existirá casos

donde la salida puede ser “1”, pero por condiciones ambientales esos casos

son imposibles que sucedan.

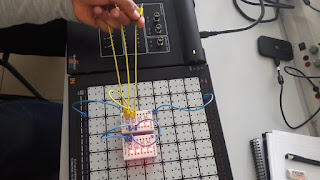

- En las pruebas de funcionamiento del circuito, el led final que representaba al toldo no encendía por un problema de conductividad en uno de los conectores empleados.

- Se observo que las compuertas lógicas ayudan a combinar distintas funciones que permiten solucionar los problemas.

- Se observo que el programa virtual ayuda a encontrar las soluciones rápidamente sin necesidad de estar haciendo el mapa de Karnaugh.

- Es necesario hacer una tabla de verdad en una hoja para luego pasarla al programa que realiza el mapa de Karnaugh.

- Se realizó la tabla de verdad empleando

las 4 variables y cumpliendo con cada una de las características que

solicitaba el problema.

- Se logró obtener la ecuación

simplificada y el mapa de Karnaugh mediante el software en línea www.32x8.com.

- Se utilizó correctamente el programa

proteus para realizar y ejecutar las simulaciones del circuito

electrónico.

- En el desarrollo del laboratorio se

identificó las puertas lógicas empleadas, su simbología y su

comportamiento en la simulación del circuito electrónico con el programa

proteus.

- Se demostró la importancia de obtener conocimientos de electrónica digital para emplearla en trabajos de automatización.

- El mapa de Karnaugh virtual ayudo a resolver las condiciones que nos pedía el laboratorio.

- Se cumplieron las funciones necesarias para resolver el circuito lógico que el laboratorio nos pedía.

- Se culmino todo el laboratorio correctamente sin problemas y se pudo utilizar las compuertas lógicas mediante un software.